Forward-looking: Samsung announced the development of its new DDR5 memory chips, a key technology for what the corporation thinks will be the upcoming expansion of "next-generation computing." The new chips bring more performance and energy efficiency to the table, even though they need an expensive EUV-based process for manufacturing.

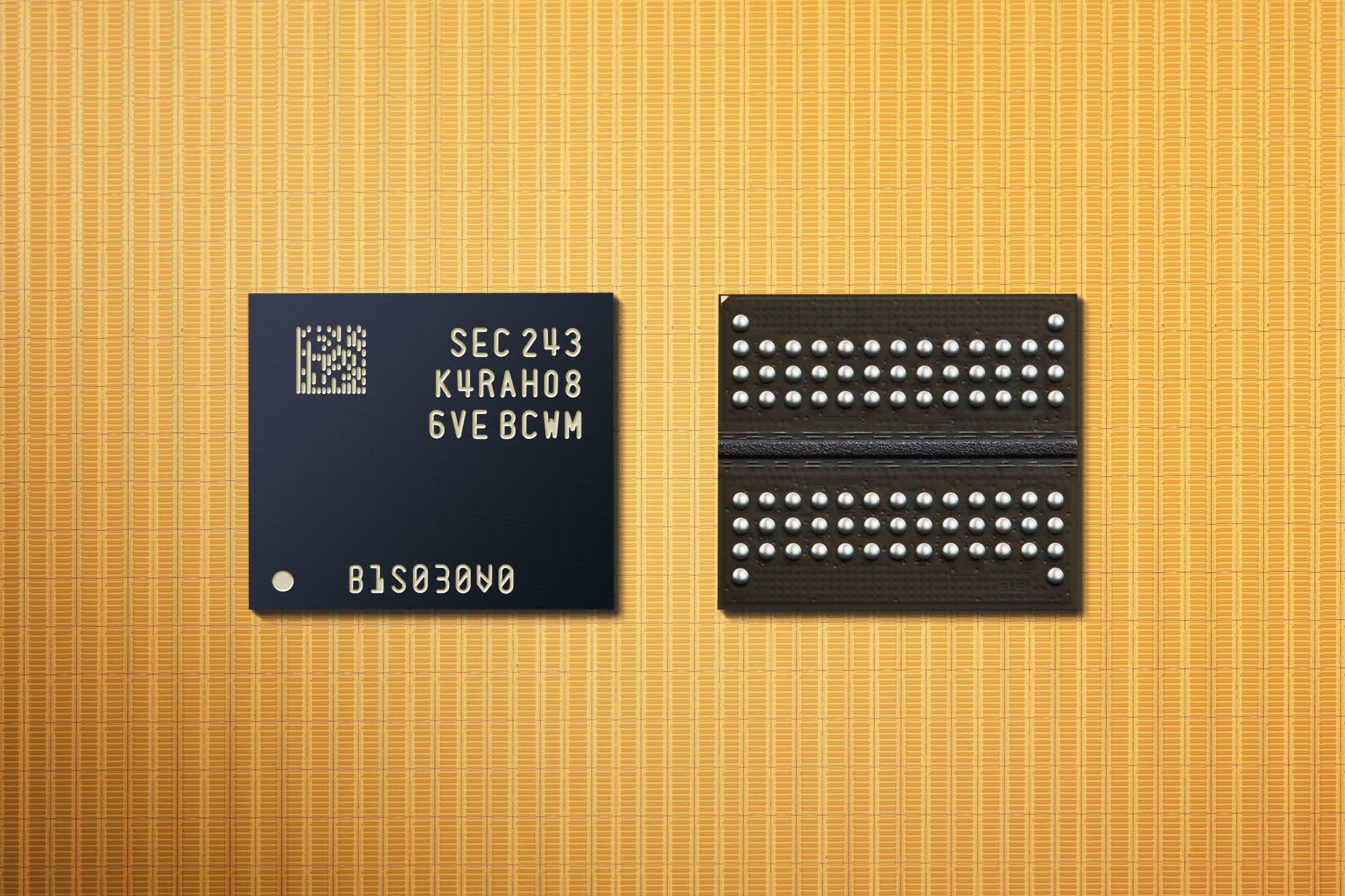

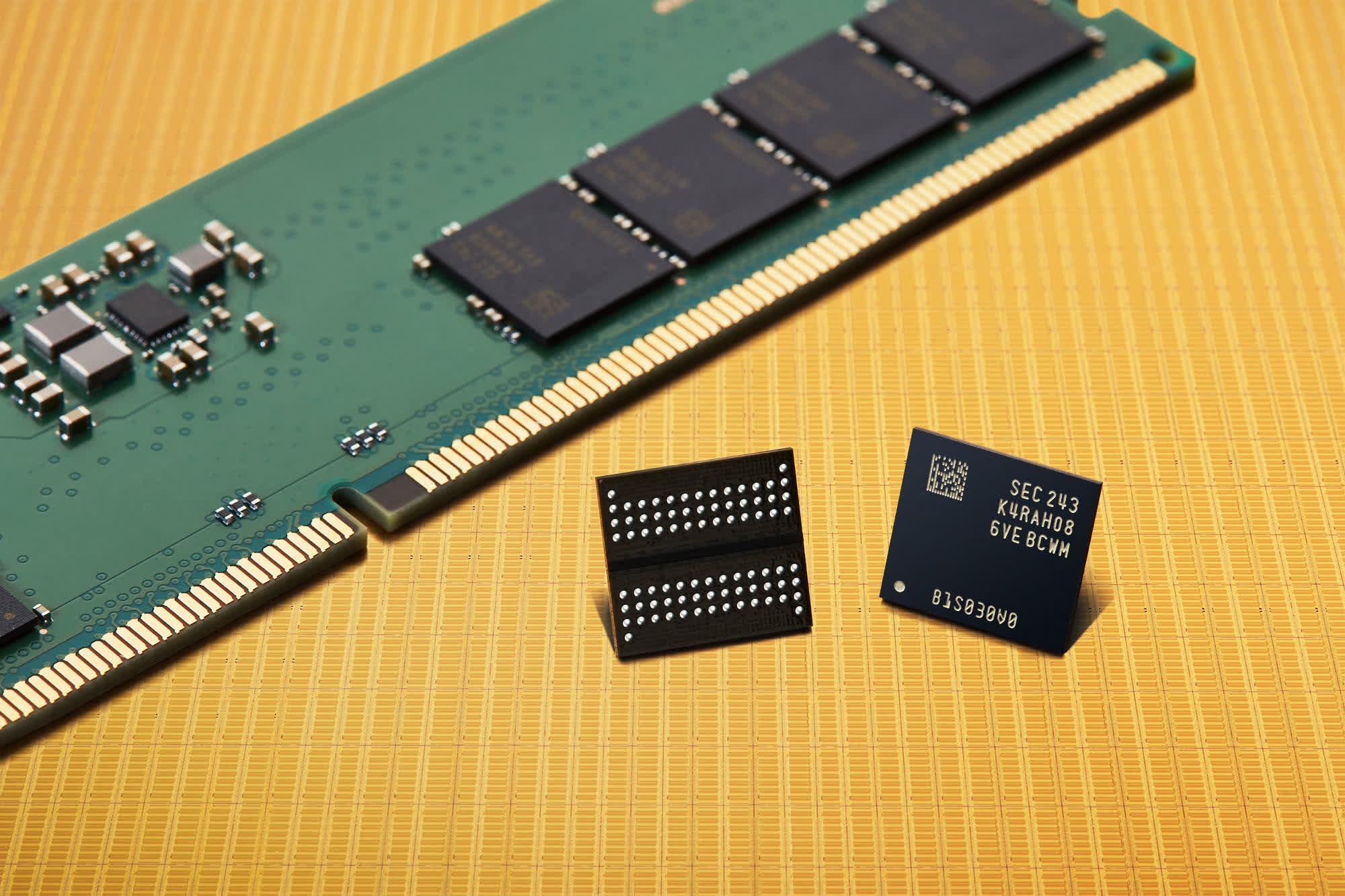

Working together with AMD, Samsung has completed the development of its 16-gigabit DDR5 DRAM chips, which will use the "industry's first 12 nanometer-class process technology." The Korean company describes these new chips as a "technological leap" for the industry; AMD helped with product evaluation for compatibility with Zen-based CPUs.

Leveraging the latest DDR5 standard, Samsung explains, the new chips will unlock speeds of up to 7.2 gigabits per second (Gbps). This would allow the new RAM modules to process two 30-gigabyte Ultra HD movies in just one second.

The 12nm chips are manufactured with a multi-layer extreme ultraviolet (EUV) lithography process, which is more expensive than deep ultraviolet (DUV) lithography machinery traditionally used for memory production. Samsung also used a new high-κ dielectric material that increases cell capacitance, and a proprietary design technology that improves critical circuit characteristics.

The 12nm chips offer the industry's highest die density, enabling a 20 percent gain in wafer productivity. The new DRAM chips are also exceptionally fast and energy efficient, consuming up to 23 percent less power than previous DRAM products.

Samsung will begin mass production of its 12nm DDR5 chips in 2023, with plans to broaden the company's DRAM lineup built on the new technology. The market segments Samsung is targeting include next-generation computing, data centers and AI-driven systems. Companies working in those markets will then have access to faster performance while increasing sustainability and power efficiency.

Jooyoung Lee, Executive Vice President of DRAM Product & Technology at Samsung Electronics, said the company's "12nm-range DRAM will be a key enabler in driving market-wide adoption of DDR5 DRAM."

Joe Macri, Senior VP at AMD, highlighted how "innovation often requires close collaboration with industry partners to push the bounds of technology." The new DDR5 chips will be optimized and validated on the Zen platform from the get go, meaning the Santa Clara corporation wants to keep the edge over competitors in supporting the latest DDR5 standards and speeds.